producten Categorie

- FM Transmitter

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV zender

- 0-50w 50-1kw 2kw-10kw

- FM-antenne

- TV-antenne

- antenne Accessory

- Kabel connector Vermogen Splitter eenheidsbelasting

- RF Transistor

- Laboratoriumvoedingen

- audio Uitrustingen

- DTV Front End Equipment

- Link System

- STL-systeem Magnetron Link systeem

- FM-radio

- Krachtmeter

- Andere producten

- Speciaal voor Coronavirus

producten Tags

FMUSER sites

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikaans

- sq.fmuser.net -> Albanees

- ar.fmuser.net -> Arabisch

- hy.fmuser.net -> Armenian

- az.fmuser.net -> Azerbeidzjaans

- eu.fmuser.net -> Baskisch

- be.fmuser.net -> Wit-Russisch

- bg.fmuser.net -> Bulgarian

- ca.fmuser.net -> Catalaans

- zh-CN.fmuser.net -> Chinees (vereenvoudigd)

- zh-TW.fmuser.net -> Chinees (traditioneel)

- hr.fmuser.net -> Kroatisch

- cs.fmuser.net -> Tsjechisch

- da.fmuser.net -> Deens

- nl.fmuser.net -> Nederlands

- et.fmuser.net -> Ests

- tl.fmuser.net -> Filipijns

- fi.fmuser.net -> Fins

- fr.fmuser.net -> Frans

- gl.fmuser.net -> Galicisch

- ka.fmuser.net -> Georgisch

- de.fmuser.net -> Duits

- el.fmuser.net -> Greek

- ht.fmuser.net -> Haïtiaans Creools

- iw.fmuser.net -> Hebreeuws

- hi.fmuser.net -> Hindi

- hu.fmuser.net -> Hungarian

- is.fmuser.net -> IJslands

- id.fmuser.net -> Indonesisch

- ga.fmuser.net -> Iers

- it.fmuser.net -> Italian

- ja.fmuser.net -> Japans

- ko.fmuser.net -> Koreaans

- lv.fmuser.net -> Lets

- lt.fmuser.net -> Lithuanian

- mk.fmuser.net -> Macedonisch

- ms.fmuser.net -> Maleis

- mt.fmuser.net -> Maltees

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> Perzisch

- pl.fmuser.net -> Pools

- pt.fmuser.net -> Portugees

- ro.fmuser.net -> Roemeens

- ru.fmuser.net -> Russisch

- sr.fmuser.net -> Servisch

- sk.fmuser.net -> Slowaaks

- sl.fmuser.net -> Slovenian

- es.fmuser.net -> Spaans

- sw.fmuser.net -> Swahili

- sv.fmuser.net -> Zweeds

- th.fmuser.net -> Thai

- tr.fmuser.net -> Turks

- uk.fmuser.net -> Oekraïens

- ur.fmuser.net -> Urdu

- vi.fmuser.net -> Vietnamese

- cy.fmuser.net -> Welsh

- yi.fmuser.net -> Jiddisch

Wat is halve opteller: schakelschema en zijn toepassingen

Date:2021/10/18 21:55:58 Hits:

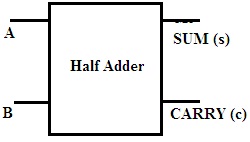

Half Adder is van het soort basis digitaal circuit. Eerder zijn er verschillende bewerkingen uitgevoerd in analoge circuits. Na de ontdekking van digitale elektronica worden er soortgelijke bewerkingen in uitgevoerd. De digitale systemen worden als effectief en betrouwbaar beschouwd. Van de verschillende bewerkingen is rekenkunde een van de meest prominente bewerkingen. Het omvat optellen, aftrekken, vermenigvuldigen en delen. Het is echter al bekend dat het een computer kan zijn, elk elektronisch gadget zoals een rekenmachine kan wiskundige bewerkingen uitvoeren. Deze bewerkingen worden uitgevoerd zijn bestaat uit binaire waarden. Dit is mogelijk door de aanwezigheid van bepaalde circuits erin. Deze circuits worden binaire optellers en aftrekkers genoemd. Dit type circuits is ook ontworpen voor de binaire codes, Excess-3-codes en andere codes. Verdere binaire optellers zijn ingedeeld in twee typen. Dit zijn: halve opteller en volledige opteller Wat is een halve opteller? Een digitale elektronische schakeling die functioneert om de optelling op de binaire getallen uit te voeren, wordt gedefinieerd als halve opteller. Het proces van optellen is niet mogelijk, het enige verschil is het gekozen nummersysteem. Er bestaat alleen 0 en 1 in het binaire nummeringssysteem. Het gewicht van het getal is volledig gebaseerd op de posities van de binaire cijfers. Van die 1 en 0 wordt 1 behandeld als het grootste cijfer en 0 als het kleinere. Het blokschema van deze opteller is Halve opteller Halve opteller Circuitdiagram Een halve opteller bestaat uit twee ingangen en produceert twee uitgangen. Het wordt beschouwd als de eenvoudigste digitale schakelingen. De ingangen van deze schakeling zijn de bits waarop de optelling moet worden uitgevoerd. De verkregen outputs zijn de som en de carry.

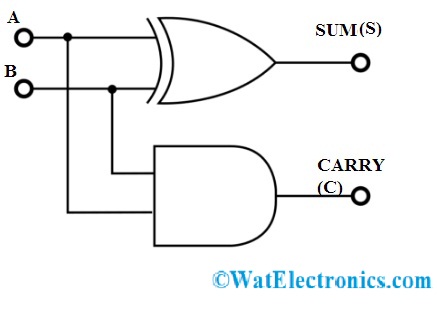

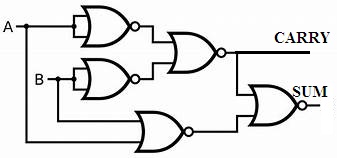

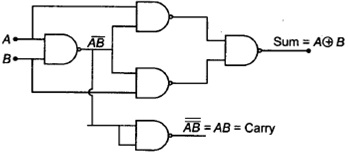

Halve opteller Halve opteller Circuitdiagram Een halve opteller bestaat uit twee ingangen en produceert twee uitgangen. Het wordt beschouwd als de eenvoudigste digitale schakelingen. De ingangen van deze schakeling zijn de bits waarop de optelling moet worden uitgevoerd. De verkregen outputs zijn de som en de carry.  Halve opteller Het circuit van deze opteller bestaat uit twee poorten. Het zijn EN- en XOR-poorten. De toegepaste ingangen zijn hetzelfde voor beide poorten die in het circuit aanwezig zijn. Maar de uitvoer wordt van elke poort genomen. De uitvoer van de XOR-poort wordt SUM genoemd en de uitvoer van EN is bekend CARRY.Half Adder Truth Table Om de relatie van de verkregen uitvoer met de toegepaste invoer te verkrijgen, kan worden geanalyseerd met behulp van een tabel die bekend staat als Truth Table.

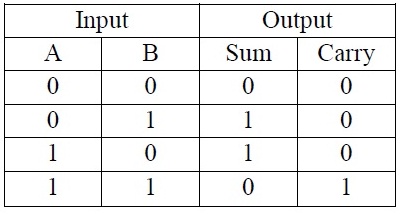

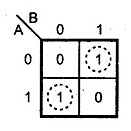

Halve opteller Het circuit van deze opteller bestaat uit twee poorten. Het zijn EN- en XOR-poorten. De toegepaste ingangen zijn hetzelfde voor beide poorten die in het circuit aanwezig zijn. Maar de uitvoer wordt van elke poort genomen. De uitvoer van de XOR-poort wordt SUM genoemd en de uitvoer van EN is bekend CARRY.Half Adder Truth Table Om de relatie van de verkregen uitvoer met de toegepaste invoer te verkrijgen, kan worden geanalyseerd met behulp van een tabel die bekend staat als Truth Table. Halve opteller waarheidstabel Uit de bovenstaande waarheidstabel zijn de punten als volgt duidelijk: Als A=0, B=0, dat wil zeggen dat beide inputs 0 zijn. Dan zijn zowel de outputs SUM als CARRY 0. Van de twee inputs die worden toegepast als iemand de invoer is 1 dan is de SUM e1 maar de CARRY is 0. Als beide ingangen 1 zijn, is de SUM gelijk aan 0 en is de CARRY gelijk aan 1. Op basis van de toegepaste ingangen gaat de halve opteller verder met de bewerking van optelling. Vergelijking De vergelijking voor dit type circuits kan worden gerealiseerd door de concepten Sum of Products (SOP) en Products of Sum (POS). De Booleaanse vergelijking voor dit type circuits bepaalt de relatie tussen de toegepaste invoer en de verkregen uitvoer. Om de vergelijking te bepalen, worden de k-kaarten getekend op basis van de waarheidstabelwaarden. Het bestaat uit twee vergelijkingen omdat er twee logische poorten in worden gebruikt. De k-map van de carry is

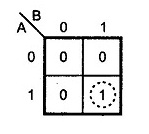

Halve opteller waarheidstabel Uit de bovenstaande waarheidstabel zijn de punten als volgt duidelijk: Als A=0, B=0, dat wil zeggen dat beide inputs 0 zijn. Dan zijn zowel de outputs SUM als CARRY 0. Van de twee inputs die worden toegepast als iemand de invoer is 1 dan is de SUM e1 maar de CARRY is 0. Als beide ingangen 1 zijn, is de SUM gelijk aan 0 en is de CARRY gelijk aan 1. Op basis van de toegepaste ingangen gaat de halve opteller verder met de bewerking van optelling. Vergelijking De vergelijking voor dit type circuits kan worden gerealiseerd door de concepten Sum of Products (SOP) en Products of Sum (POS). De Booleaanse vergelijking voor dit type circuits bepaalt de relatie tussen de toegepaste invoer en de verkregen uitvoer. Om de vergelijking te bepalen, worden de k-kaarten getekend op basis van de waarheidstabelwaarden. Het bestaat uit twee vergelijkingen omdat er twee logische poorten in worden gebruikt. De k-map van de carry is  K-Map AND GateDe uitvoervergelijking van CARRY wordt verkregen uit de AND-poort.C=A.BDe Booleaanse expressie voor de SUM wordt gerealiseerd door de SOP-vorm. Daarom is de K-map voor de SUM

K-Map AND GateDe uitvoervergelijking van CARRY wordt verkregen uit de AND-poort.C=A.BDe Booleaanse expressie voor de SUM wordt gerealiseerd door de SOP-vorm. Daarom is de K-map voor de SUM K-Map for Sum (XOR)De vastgestelde vergelijking is S= A⊕ BToepassingenDe toepassingen van deze basisopteller zijn als volgt. Om optellingen uit te voeren op binaire bits, geeft de rekenkundige en logische eenheid in de computer de voorkeur aan deze optelschakeling. De combinatie van halve optellerschakelingen leidt aan de vorming van het Full Adder-circuit. Deze logische circuits hebben de voorkeur bij het ontwerpen van rekenmachines. Om de adressen en tabellen te berekenen, hebben deze circuits de voorkeur. In plaats van alleen optellen, kunnen deze circuits verschillende toepassingen in digitale circuits aan. Verder wordt dit het hart van digitale elektronica.VHDL-codeDe VHDL-code voor het Half Adder-circuit islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;architectuurgegevens van half_adder isbeginsum<= a xor b;carry <= a en b;end data;FAQs1. Wat bedoelt u met opteller? De digitale circuits waarvan het enige doel is om optelling uit te voeren, staan bekend als optellers. Dit zijn de belangrijkste componenten van ALU's. Optellers werken naast de verschillende formaten van getallen. De uitgangen van de optellers zijn de som en de carry.2. Wat zijn de beperkingen van Half Adder? De carry-bit die is gegenereerd op basis van de vorige bit kan niet worden toegevoegd, dit is de beperking van deze opteller. Om optelling voor meerdere bits uit te voeren, kunnen deze circuits niet de voorkeur hebben.3. Hoe een halve opteller te implementeren met behulp van NOR-poort? De implementatie van dit type opteller kan ook worden gedaan met behulp van de NOR-poort. Dit is een andere Universele Poort.

K-Map for Sum (XOR)De vastgestelde vergelijking is S= A⊕ BToepassingenDe toepassingen van deze basisopteller zijn als volgt. Om optellingen uit te voeren op binaire bits, geeft de rekenkundige en logische eenheid in de computer de voorkeur aan deze optelschakeling. De combinatie van halve optellerschakelingen leidt aan de vorming van het Full Adder-circuit. Deze logische circuits hebben de voorkeur bij het ontwerpen van rekenmachines. Om de adressen en tabellen te berekenen, hebben deze circuits de voorkeur. In plaats van alleen optellen, kunnen deze circuits verschillende toepassingen in digitale circuits aan. Verder wordt dit het hart van digitale elektronica.VHDL-codeDe VHDL-code voor het Half Adder-circuit islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;architectuurgegevens van half_adder isbeginsum<= a xor b;carry <= a en b;end data;FAQs1. Wat bedoelt u met opteller? De digitale circuits waarvan het enige doel is om optelling uit te voeren, staan bekend als optellers. Dit zijn de belangrijkste componenten van ALU's. Optellers werken naast de verschillende formaten van getallen. De uitgangen van de optellers zijn de som en de carry.2. Wat zijn de beperkingen van Half Adder? De carry-bit die is gegenereerd op basis van de vorige bit kan niet worden toegevoegd, dit is de beperking van deze opteller. Om optelling voor meerdere bits uit te voeren, kunnen deze circuits niet de voorkeur hebben.3. Hoe een halve opteller te implementeren met behulp van NOR-poort? De implementatie van dit type opteller kan ook worden gedaan met behulp van de NOR-poort. Dit is een andere Universele Poort. Halve opteller met NOR-poorten4. Hoe Half Adder te implementeren met behulp van NAND Gate? De NAND-poort is een van de soorten universele poorten. Het geeft aan dat elk soort circuitontwerp mogelijk is door het gebruik van NAND-poorten.

Halve opteller met NOR-poorten4. Hoe Half Adder te implementeren met behulp van NAND Gate? De NAND-poort is een van de soorten universele poorten. Het geeft aan dat elk soort circuitontwerp mogelijk is door het gebruik van NAND-poorten. Half AdderVan het bovenstaande circuit kan de carry-output worden gegenereerd door de output van een NAND-poort op de ingang toe te passen als een andere NAND-poort. Dat is niets anders dan bekend bij de uitvoer verkregen van de EN-poort. De uitvoervergelijking van SUM kan worden gegenereerd door de uitvoer van de initiële NAND-poort samen met de individuele ingangen van A en B toe te passen op verdere NAND-poorten. Ten slotte worden de door die NAND-poorten verkregen uitgangen weer aan de poort toegevoerd. Daarom wordt de uitvoer voor de SUM gegenereerd. Daarom kan de basisopteller in het digitale circuit worden ontworpen door verschillende logische poorten te gebruiken. Maar de optelling van meerdere bits wordt ingewikkeld en wordt beschouwd als de beperking van de halve opteller. Kunt u beschrijven welke IC wordt gebruikt voor de incrementbewerking in praktische tellers?

Half AdderVan het bovenstaande circuit kan de carry-output worden gegenereerd door de output van een NAND-poort op de ingang toe te passen als een andere NAND-poort. Dat is niets anders dan bekend bij de uitvoer verkregen van de EN-poort. De uitvoervergelijking van SUM kan worden gegenereerd door de uitvoer van de initiële NAND-poort samen met de individuele ingangen van A en B toe te passen op verdere NAND-poorten. Ten slotte worden de door die NAND-poorten verkregen uitgangen weer aan de poort toegevoerd. Daarom wordt de uitvoer voor de SUM gegenereerd. Daarom kan de basisopteller in het digitale circuit worden ontworpen door verschillende logische poorten te gebruiken. Maar de optelling van meerdere bits wordt ingewikkeld en wordt beschouwd als de beperking van de halve opteller. Kunt u beschrijven welke IC wordt gebruikt voor de incrementbewerking in praktische tellers?

Laat een bericht achter

Message List

Reacties Laden ...